HIL Read Digital Timebase

Reads the specified digital channels at the sampling rate of the model and acts as a timebase for the model.

Library

QUARC Targets/Data Acquisition/Generic/Timebases MATLAB Command Line Click to copy the following command line to the clipboard. Then paste it in the MATLAB Command Window: qc_open_library('quarc_library/Data Acquisition/Generic/Timebases')

Description

The HIL Read Digital Timebase block reads the specified digital channels at every sampling instant. The timebase for the model is provided by the block itself. Only one HIL Timebase block may appear in the model. Multiple timebases for a model are not supported.

All the channels which will be used as digital inputs must be entered

in the Digital input channels field of the

Digital Inputs pane in the HIL Initialize

block's parameters dialog. Doing so ensures that those channels will be configured as inputs when using a card for

which the digital I/O lines are programmable as inputs or outputs. Failure to configure these channels

in the Digital input channels field as inputs may result in the

HIL Read Digital Timebase block failing to read those inputs.

All the channels which will be used as digital inputs must be entered

in the Digital input channels field of the

Digital Inputs pane in the HIL Initialize

block's parameters dialog. Doing so ensures that those channels will be configured as inputs when using a card for

which the digital I/O lines are programmable as inputs or outputs. Failure to configure these channels

in the Digital input channels field as inputs may result in the

HIL Read Digital Timebase block failing to read those inputs.

Input Ports

This block has no input ports.

Output Ports

The number of output ports depends on the Vector output parameter. If this option is checked then the output is a vector containing the states read from the channels specified in the Channels parameter. Otherwise there is one output port for each channel and each port outputs the state read from the corresponding channel. Refer to the documentation on the Vector output parameter below for more details.

Data Type Support

The HIL Read Digital Timebase block outputs signals of any of the built-in Simulink datatypes, except fixed point. See the Signal Data Types pane below for information on how the output data type is determined.

Parameters and Dialog Box

Individual Panes

Main Pane

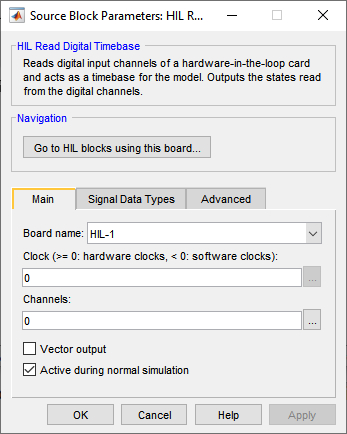

The Main pane of the dialog appears as follows:

Board Name

The name of the board whose digital channels will be read. Boards are configured using the HIL Initialize block. Place an HIL Initialize block in your diagram to add a board name to the list.

Clock

The clock to use as a basis for the timebase. In general, both system clocks and hardware clocks specific to the board are supported. This parameter must be a scalar. A positive value indicates a hardware clock. For example, enter 0 for HARDWARE_CLOCK_0, 1 for HARDWARE_CLOCK_1, etc. The number of hardware clocks available depends on the board selected. A negative value indicates a system clock. For example, enter -1 for SYSTEM_CLOCK_1, -2 for SYSTEM_CLOCK_2, etc. The sampling rate for the block is determined by the fundamental sampling rate of the model, which is the sampling time entered in the Fixed step size field of the Solver pane of the Configuration parameters. Refer to Clocks for more information.

Select a board type from the list for board-specific details:

Channels

The digital channels to read. The number of channels available depends on the board selected. Refer to Channels for more information.

Select a board type from the list for board-specific details:

Vector output

If this option is checked then the block will have a single vector output with one element in the vector for each channel. The states read from each channel will appear in the vector in the same order as the channels in the Channels parameter.

If this option is not checked then the block will have one output for each channel. The output ports will appear in the same order as the channels in the Channels parameter. Each port will be labeled with the corresponding channel number.

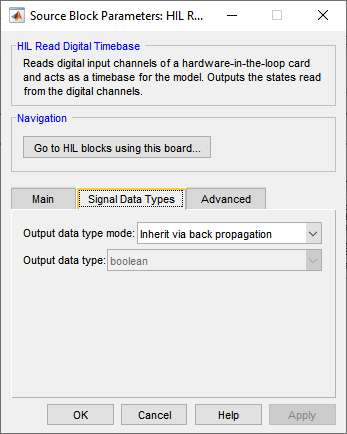

Signal Data Types Pane

The Signal Data Types pane of the dialog appears as follows:

Output data type mode

Sets the data type of the output to be inherited by back propagation or to be specified explicitly in the dialog.

If back propagation is selected then the data type of the output will be determined

by the block to which the output is connected. If the output is not connected or

it is connected to a block which supports multiple datatypes, then the output data

type will be boolean.

Otherwise the data type of the output can be specified explicitly using the Output data type parameter.

Output data type

Sets the data type of the output explicitly.

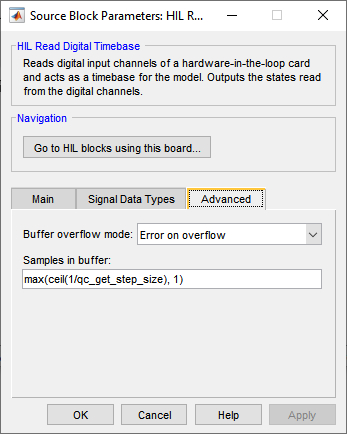

Advanced Pane

The Advanced pane of the dialog appears as follows:

Buffer overflow mode (tunable offline)

The buffer overflow mode determines what happens when the task buffer overflows. The default behaviour is to stop the model with an error because buffer overflow means that the foreground task has not been able to keep up with the timebase from the hardware. The Error on overflow option results in this behaviour.

The Overwrite on overflow option causes new samples to overwrite the oldest samples in the buffer when the buffer would overflow. In this case, these oldest samples will be lost, but the model will continue to run.

The Discard on overflow option discards new samples if there is no room in the task buffer. In this case, the older samples are preserved and will be output from the block in proper sequence. New samples are lost, but the model will continue to run.

The Wait on overflow option is only used with simulated cards. Simulated cards can be implemented in a separate model using the HIL Simulation block. When the Wait on overflow option is specified and the task buffer is full, it causes the model simulating the card to block until the model containing the HIL Read Digital Timebase block removes a sample from the task buffer, making room for the new sample. This allows the two models to be synchronized and is generally only useful in normal simulation, where sample time performance is poor. If this option is specified then a value of 1 is recommended for the Samples in buffer option. More complete synchronization is provided by the Synchronize option, described below, which is recommended when using simulated cards.

The Synchronize option is also only used with simulated cards. Simulated cards can be implemented in a separate model using the HIL Simulation block. When the Synchronize option is specified it causes the model to synchronize with the model simulating the card. This is generally only useful in normal simulation, where sample time performance is poor.

Samples in buffer

The number of samples in the task buffer. Timebase blocks are implemented as HIL tasks. Tasks operate as separate "threads" in the driver for the card that read data from the hardware at a given rate. The data read is stored in the task buffer. If the task buffer overflows then the block typically stops the model with an error, although this behaviour can be changed using the Buffer overflow mode parameter. Each time the block executes, it reads one sample from the task buffer. If there is no data in the task buffer then it waits until a sample arrives. Hence, the block synchronizes the diagram to the sampling rate of the task. Making the number of samples in the task buffer greater than one allows the sampling rate to temporarily exceed one sampling interval, which is useful for normal simulation.

Some boards restrict the number of samples that may be specified. Select a board type from the list for board-specific details:

Targets

|

Target Name |

Compatible* |

Model Referencing |

Comments |

|---|---|---|---|

|

Yes |

Not supported in a referenced model. Use in top-level model only. |

Only one HIL Timebase block is allowed in a model. |

|

|

Yes |

Not supported in a referenced model. Use in top-level model only. |

Only one HIL Timebase block is allowed in a model. |

|

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

Yes |

Yes |

||

|

No |

No |

Not currently supported. |

|

|

Yes |

Not supported in a referenced model. Use in top-level model only. |

Last fully supported in QUARC 2018. Only one HIL Timebase block is allowed in a model. |

|

|

Rapid Simulation (RSIM) Target |

Yes |

Yes |

Only one HIL Timebase block is allowed in a model. |

|

S-Function Target |

No |

N/A |

Old technology. Use model referencing instead. |

|

Normal simulation |

Yes |

Yes |

Due to safety and liability concerns, the hardware may not be accessed during normal simulation. |

See Also

Copyright ©2025 Quanser Inc. This page was generated 2025-11-01. Submit feedback to Quanser about this page.

Link to this page.